黑燈工廠賦能 小米從研發到生產的全鏈路自主創新

小米在智能科技領域持續深化布局,通過引入“黑燈工廠”模式,實現了從產品研發到生產制造的全鏈路自主化。這一轉變不僅提升了小米的供應鏈韌性,更彰顯了其在技術創新與智能制造領域的戰略決心。

在研發層面,小米依托黑燈工廠的數字化基礎設施,加速了技術開發與產品迭代的閉環。通過人工智能、物聯網與大數據分析,研發團隊能夠實時模擬產品性能、優化設計方案,并將數據直接同步至生產線,顯著縮短了從概念到原型的時間。例如,在智能手機與智能家居設備的開發中,小米已實現核心算法與硬件設計的深度融合,確保技術自主性與產品差異化。

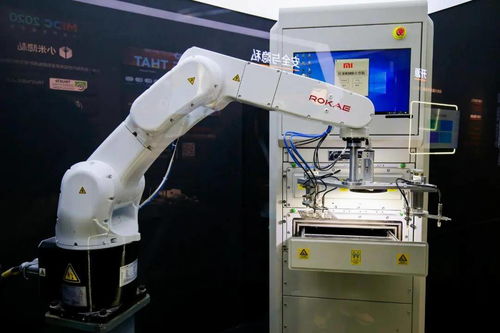

生產環節的變革尤為顯著。黑燈工廠以高度自動化的“無人化”生產為核心,通過機器人、智能傳感與自適應控制系統,實現了24小時不間斷運作。小米的北京亦莊智能工廠便是典型代表,該工廠覆蓋了SMT貼片、整機組裝到質量檢測的全流程,人力依賴度降至極低水平。這種模式不僅提升了生產效率與產品一致性,還通過實時數據反饋不斷優化工藝,使小米能夠快速響應市場需求變化。

全鏈條自主化助力小米構建了技術護城河。在智能科技領域,小米已逐步突破芯片設計、傳感器技術與操作系統等關鍵環節,減少對外部供應鏈的依賴。例如,澎湃系列芯片的研發與黑燈工廠的生產協同,確保了核心元器件自主可控;而在AIoT生態中,小米通過統一的技術平臺,實現了智能設備間的無縫協作與數據互通。

隨著5G、邊緣計算與人工智能的深度融合,小米的黑燈工廠模式有望進一步擴展至更廣泛的智能科技產品線。從研發創新到智能制造,小米正以全鏈路自主化為支點,推動中國智能科技產業向高端化、智能化邁進。

如若轉載,請注明出處:http://www.mamifa.cn/product/35.html

更新時間:2026-04-28 10:35:59